Elementos seleccionados

Capítulo I

Elementos seleccionados

A

continuación se facilita una descripción de los

elementos del sistema y sus relaciones, para lograr una

visión de conjunto.

|

ADC0808

Conversor Analógico-Digital de 8 Bits

ADC0808, Conversor

Analógico-Digital de 8 Bit , de la casa “National

semiconductor”.

Justificación:

Este es un circuito conversor A/D de 8 entradas, de la cuales

sólo utilizaremos una para controlar la intensidad media y

la intensidad eficaz. Pudiendo haber elegido otro aprovechando

más sus características, la elección

de éste se basa en:

• Su fácil interface con todos los

microprocesadores.

• El no requerimiento de ajuste de cero o escala completa.

• Su rapidez y gran precisión en la

conversión.

En la configuración elegida para el esquema general recibe

una señal analógica proveniente del filtro

paso-bajo (intensidad media) y otra del conversor a valor eficaz AD536

(intensidad eficaz ).

Para elegir que señal queremos controlar en cada momento una

de las entradas de selección las conectamos con el Puerto 1

del micro, para que con un valor 0 ó 1 seleccione la

señal analógica de la que queremos obtener su

valor en digital por la salida de conversor A/D. Cuando esta

señal supere los valores establecidos como

máximos, activará el microprocesador.

|

AD536A

Integrated Circuit True RMS-to-DC Converter

AD536A, Integrated Circuit True

RMS-to-DC Converter, de la casa “Anlog Devices”.

Justification:

Se eligió la configuración del AD536A de la

figura 7 (ver ANEXO A de este circuito).

La principal causa es:

• Reduce con el filtro exterior de dos polos el rizado de

salida alterna (AC), consiguiendo una gran mejoría en la

precisión de la medida que nos compensa el aumento del

tiempo que se produce en la realización de la

conversión (RMS a DC).

Una vez realizada la elección, explicaremos más

detalladamente el funcionamiento:

El convertidor de valor eficaz a continuo, recibe en su entrada una

señal con componente AC, mandada por el amplificador

operacional en montaje diferencial, en su interior en el divisor

cuadrático medio el AD536 toma continuamente la muestra para

valorar su tensión eficaz y trasladar ese valor a la salida

en continua (DC), a través del filtro externo de dos polos

conseguiremos que ese valor en la salida tenga el mínimo

error, eso es, que lleve una mínima componente de AC.

|

OP07

Ultralow FOCET Voltaje Operational Amplifier

OP07, Ultralow FOCET Voltaje

Operational Amplifier, de la casa “Analog Devices”.

Justificación:

Este dispositivo se utilizara en dos configuraciones, como amplificador

diferencial y como filtro paso bajo.

a) amplificador diferencial.

El amplificador operacional diferencial está conectado a una

resistencia de sensado, la cual pretende, a través de su

bajo valor, no influir en el valor de corriente que esté

entregando el puente H en todo momento (recordar Intensidad =

Tensión / Resistencia), apreciando también por

esta fórmula que en ella habrá un

pequeño valor de caída de tensión (0.2

voltios a 1.5 voltios * ver cálculos del amplificador

operacional diferencial*).

La elección del amplificador operacional en montaje

diferencial es para amplificar esta señal,

intentándola llevar a unos valores de tensión

mayores con los que se pueda trabajar mejor, influyendo menos el ruido

y las capacidades parásitas.

b) Filtro paso bajo.

Hemos elegido un filtro paso-bajo activo de primer orden porque es muy

estable y no tiene peligro de entrar en oscilaciones.

Este circuito pretende eliminar la

componente de alterna que lleva la señal entregada por el

amplificador operacional diferencial, esto se realiza calculando el

filtro paso-bajo para una frecuencia de corte de 1 hertzio,

así obtendremos en su salida un nivel de tensión

continua correspondiente a la corriente media que demanda el motor, por

la relación de ganancia ofrecida por el amplificador

operacional diferencial, pues a este filtro le configuramos en montaje

seguidor de emisor para que su ganancia sea 1, no modificando el nivel

de tensión de la señal entregada por el

amplificador operacional.

|

Alarma

por temperatura

Interruptor térmico

Alarma por temperatura.

Este circuito está basado en la utilización de un

interruptor térmico, su funcionamiento sería el

siguiente:

a) Si la temperatura es inferior a (70 ± 5) ºC, el

interruptor térmico permanecerá abierto,

llegándole a la patilla de interrupción del

microprocesador INT1 activa nivel bajo, un nivel alto (5 voltios), lo

que significa que el microprocesador no indicará un fallo de

temperatura.

b) Si la temperatura del disipador es superior a (70 ± 5)

ºC, el interruptor térmico cerrará su

contacto introduciendo un nivel bajo por la patilla de

interrupción INT1 del microprocesador, dejándola

activada, indicando que existe temperatura elevada en los mosfets.

Esta señal llegara a la patilla de interrupción

INT1 a través de un Octoacoplador para separar la

señal del circuito de potencia.

Hasta que no caiga la temperatura 50 ºC (ver

características del interruptor térmico en ANEXO

A) no volverá a su posición natural de

normalmente abierto.

|

Sistema

de alarmas

Funcionamiento

|

Funcionamiento del

esquema completo de alarmas y errores.

El fin perseguido por este esquema es el de conseguir que a un

microprocesador le llegue en todo momento el valor de corriente medio y

eficaz, que demande el puente H para que cuando estos valores superen a

los establecidos como máximos, el microprocesador a

través de su bit de interrupciones atienda al error y mande

las correspondientes órdenes al LM629 para que regule el

motor a un funcionamiento establecido como correcto.

Para obtener una más clara explicación vamos a

dividir las señales controladas:

- Alarma de temperatura: colocando un interruptor térmico

normalmente abierto en el disipador del puente H, activará

por la configuración de circuito únicamente el

bit de interrupciones, cuando la temperatura sea superior a la

especificada.

- Alarma por la superación de la intensidad media y alarma

por superación de la intensidad eficaz:

Ambas parten de un amplificar operacional en montaje diferencial, que

pretende aumentar la tensión que recae en la resistencia de

sensado del puente H y por una relación

tensión-corriente obtener el valor de esta

última.

- Respecto a la superación de la intensidad media: la

señal proveniente del amplificador operacional diferencial

es conducida a la entrada de un filtro paso-bajo con frecuencia de

corte de 1 Hertzio, con el propósito de eliminar el valor de

alterna de la señal de entrada y obtener en la salida del

filtro el valor de tensión de continua medio que

está entregando actualmente el puente H.

Esta señal la recibe un conversor

analógico-digital para tratarla y obtener un valor digital

con el que poder atacar al microprocesador.

- Respecto a la superación de la intensidad eficaz: la

señal recibida del amplificador operacional diferencial se

conecta a la entrada de un conversor a valor eficaz, que a su vez se

conecta a la entrada analógica de un conversor

analógico digital, para que éste la convierta en

un valor digital ejecutable por el microprocesador.

A través de una línea de dirección,

escogeremos mediante el microprocesador si queremos leer intensidad

eficaz o intensidad media.

Representación de las alarmas.

Esta se llevara a cabo por medio de un visualizador de 7 segmentos, el

cual se describirá a continuación.

|

LM7446A

DECODIFICADOR BCD A 7 SEGMENTOS

|

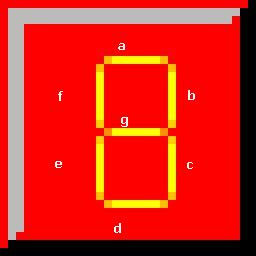

DESCRIPCIÓN GENERAL.

El 7446A y 7447A se caracterizan por salidas activas a nivel bajo

diseñadas para manejar leds de ánodo

común o indicadores incandescentes directamente; y el 7448

se caracteriza por salidas activas a nivel alto para manejar buffers de

lámparas o leds de cátodo común.

Todos los circuitos tienen controles de entrada/salida de puesta en

blanco y una entrada de pruebas de lámparas.

DESCRIPCIÓN DE FUNCIONAMIENTO.

El decodificador/excitador BDC a siete segmentos consta de puertas

NAND, buffers de entrada y siete puertas AND-OR INVERT.

Esto ofrece salidas de corriente de absorción (SINK CURRENT)

elevada con un bajo activo para excitar indicadores directamente. Siete

puertas NAND y un excitador se hallan conectadas por parejas para poder

ofrecer los datos BCD y su complemento a las siete puertas

decodificadoras AND-OR-INVERT.

La puerta restante NAND y tres buffers de entrada proporcionan la

entrada de lámpara de prueba, entrada de BLANKING salida de

RIPPLE-BLANKING y entrada RIPPLE BLANKING.

El circuito acepta información BCD (decimal codificado

binario) de 4 bits y dependiendo del estado de las entradas auxiliares,

decodifica estos datos para atacar un indicador de siete segmentos.

Los niveles de salida lógica-positiva, así como

las condiciones requeridas en las entradas auxiliares, se indican en la

tabla de verdad. Las configuraciones de salida del

decodificador/excitador están diseñadas para

aguantar las tensiones relativamente elevadas requeridas por los

indicadores de siete segmentos.

Las salidas aguantan 15 voltios con una corriente inversa

máxima de 250µA. La presentación visual

de entradas BCD por encima de 9 son símbolos

únicos para denotar las condiciones de entrada.

El decodificador/excitador lleva incorporados control

automático de CERO-BLANKING en el flanco posterior y/o

anterior (RBI y RBO).

La prueba de lámpara (LAMP TEST LT) de estos tipos puede

realizarse en cualquier momento en que el nudo BI/RBO esté

en nivel alto. Ambos contienen una entrada para contrarrestar el

BLANKING (BI), que puede utilizarse para controlar la "intensidad de la

lámpara" o para inhibir las salidas.

NOTAS:

BI/RBO está cableada AND sirviendo como entrada de BLANKING

(BI) y/o salida RIPPLE-BLANKING (RBO).

La entrada de BLANKING (BI) debe estar abierta omantenida a un nivel

alto cuando se deseen funciones de salida 0 a 15, y la entrada de

RIPPLE-BLANKING (RBI) debe estar abiera o a nivel alto si no se desea

el BLANKING de un 0 decimal.X=la entrada puede ser alta o baja.

Cuando se aplica un nivel bajo a la entrada de BLANKING

(condición forzada) todas las salidas de segmento se van a

nivel bajo independientemente del estado de cualquier otra

condición de entrada.

Cuando la entrada de RIPPLE-BLANKING (RBI) y las entradas A, B, C, y D

esté a nivel bajo, con la entrada de prueba de

lámpara a nivel alto, todas las salidas de segmento se van a

nivel alto y la salida de RIPPLE-BLANKING (RBO) se pone a nivel bajo

(condición de respuesta).

Cuando la entrada de BLANKING/salida de RIPPLE-BLANKING (BI/RBO)

esté abierta o mantenida anivel alto y se aplique un nivel

bajo a la entrada de prueba de lámpara (LAMP TEST), todas

las salidas de segmento se ponen a nivel bajo.

Todas las demás combinaciones que no están

recogidas en las notas, se refieren al funcionamiento normal del

circuito para un valor de entrada en BCD tenemos en la salida

representado decimalmente mediante un display ese valor.

|

|

Decodificador/excitador BDC a siete

segmentos.

|

ENTRADAS |

E

/ S |

SALIDAS |

|

| DECIMAL

o Función |

LT |

RBI |

D |

C |

B |

A |

BI / RBO |

a |

b |

c |

d |

e |

f |

g |

NOTA |

| 0 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0

|

0 |

0 |

0 |

0 |

0 |

1 |

A |

| 1 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

A |

| 2 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0

|

0 |

1

|

0 |

0 |

1

|

0 |

A |

| 3 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0

|

0 |

0 |

0 |

1 |

1 |

0 |

A |

| 4 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

A |

| 5 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0

|

1 |

0 |

0 |

1 |

0 |

0 |

A |

| 6 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

A |

| 7 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0

|

0 |

0 |

1 |

1 |

1 |

1 |

A |

| 8 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

A |

| 9 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0

|

0 |

0 |

1 |

1 |

0 |

0 |

A |

| 10 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

A |

| 11 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

A |

| 12 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

A |

| 13 |

1 |

x |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

A |

| 14 |

1 |

x |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

A |

| 15 |

1 |

x |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

A |

| BI |

x |

x |

x |

x |

x |

x |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

B |

| RBI |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

C |

| LT |

0 |

x |

x |

x |

x |

x |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

Designaciones

numéricas. Visualización resultante.

Donde:

|

|

|

Capítulo II

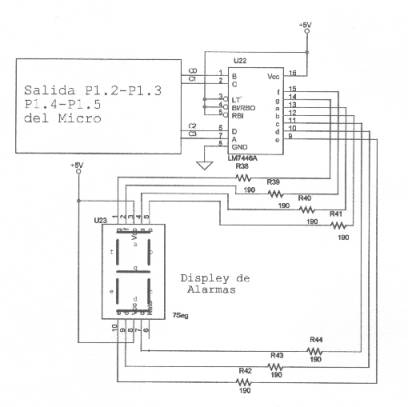

Circuito de visualización de alarmas

|

| |

Descripción

detallada del circuito de

visualización de alarmas

|

En primer lugar conectamos LT, RBI y

BI/RBO a VCC (+5 Voltios), para tenerlas a un nivel alto, necesario

para el requerido funcionamiento en BCD del 7446.

Las entradas A, B, C y D reciben las

salidas del puerto 1 del microprocesador, el cual, escribirá

en ellas ciertas combinaciones binarias según el error o el

buen funcionamiento del esquema general, quedando representadas en un

visualizador óptico (display), en un código

más inteligible para el hombre.

Seguidamente presentamos la tabla de

códigos:

| VISUALIZACIÓN |

SITUACIÓN |

| 0 |

No hay problemas |

| 1 |

Trayectoria completa con

éxito |

| 2 |

Error de desbordamiento

de datos |

| 3 |

Error de

posición |

En la siguiente figura se puede ver el

diseño utilizado.

Las diferentes patillas de un Display

de 7 segmentos son las siguientes:

| Patilla |

Segmento / Señal |

| 1 |

g |

| 2 |

f |

| 3 |

Vcc |

| 4 |

a |

| 5 |

b |

| 6 |

ánodos |

| 8 |

Vcc |

| 9 |

d |

| 10 |

e |

|

|

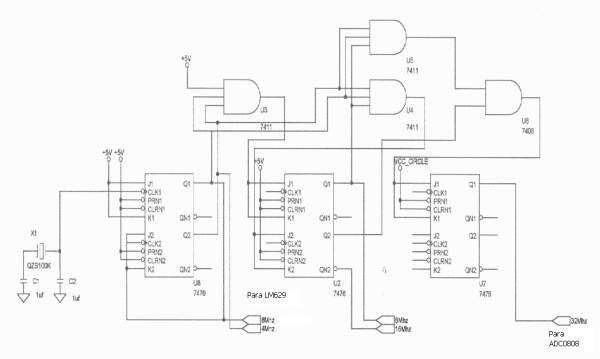

Circuitos

de reloj

|

Partiendo del

preámbulo de la obtención de un cristal de cuarzo

de 16 MHz para atacar al microprocesador, debemos obtener una

señal de reloj de 8 MHz para el LM628 y de 500KHz para el

conversor A/D ADC0808 para hacer lo propio.

Para cumplir estos objetivos y con nuestros

conocimientos, podemos apreciar que todas las frecuencias a conseguir

son submúltiplos en potencia de dos de la principal.

Por ello, cabe pensar en la utilización de contadores para

realizar una división en frecuencia, o una segunda forma,

basada en el manejo de básculas para conseguir el mismo

objetivo.

Nosotros nos hemos decantado por ésta última,

pensando en la mejor utilización de un solo tipo de

integrado como elemento principal la báscula (flip-flop

7476).

|

|

El

circuito se puede ver el la figura siguiente.

Figura 2 Esquema final del reloj

Su funcionamiento será:

| |

FF5 |

FF4 |

FF3 |

FF2 |

FF1 |

| 00 |

0 |

0 |

0 |

0 |

0 |

| 01 |

0 |

0 |

0 |

0 |

1 |

| 02 |

0 |

0 |

0 |

1 |

0 |

| 03 |

0 |

0 |

0 |

1 |

1 |

| ... |

... |

... |

... |

... |

... |

| 29 |

1 |

1 |

1 |

0 |

0 |

| 30 |

1 |

1 |

1 |

0 |

1 |

| 31 |

1 |

1 |

1 |

1 |

0 |

| 32 |

1 |

1 |

1 |

1 |

1 |

| |

f /16 |

f /8 |

f /4 |

f /2 |

f /1 |

TABLA

1 Salida del conteo codificado

El circuito consta de cinco flip-flop en serie, los cuales

están interconectados a través de puertas AND, de

forma parecida a un registro de desplazamiento.

La señal de reloj se aplica a todos los flip-flop del

contador en paralelo, con lo cual los estados de sus salidas cambian

simultáneamente.

Debido a esta disposición de la señal de reloj,

este tipo de circuito se denomina “contador

síncrono”.

La regla por la cual en la columna uno de la tabla 1existe una

alternancia continua de 1 y 0, se puede interpretar como la salida de

un flip-flop JK que se dispara continuamente.

El flip-flop JK, FF1, del esquema general se dispara cuando existe

nivel 1 en sus entradas J y K.

La columna de peso 2 de la tabla 1, también tiene una

alternancia entre 1 y 0, sólo que ahora el cambio se produce

cada dos impulsos de reloj.

Comparando las secuencias de la columna del 2 con la de la 1 se

establece que cuando la columna 1 está en lógica

1, a la llegada del próximo impulso de cómputo,

la columna del 2 cambia su estado lógico.

Esto se puede implementar conectando las dos entradas de FF2 a la

salida Q de FF1, cuya señal producirá el disparo

de FF2.

|

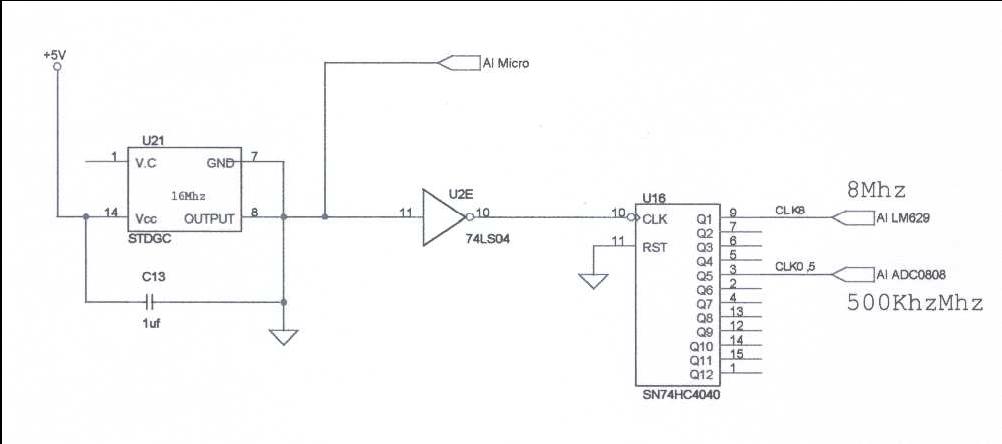

Una vez realizado este diseño,

conseguimos mejorarlo teóricamente respecto a la

utilización de un menor número de circuitos

integrados, lo que lleva consigo una mejora también respecto:

-Reducción de espacio en el diseño

práctico.

-Reducción de cableado y por consiguiente menor posibilidad

de falsos contactos.

El circuito integrado que consigue realizar el mismo trabajo es el

MM74HC4040.

Al ser este proyecto teórico, creemos más

conveniente la utilización de esta última idea,

pero damos al lector la posibilidad de las dos configuraciones por los

distintos fines y/o predilecciones que pueda tener.

Ahora nuestro objetivo es explicar el circuito de reloj realizado con

el MM74HC4040.

Su funcionamiento es sencillo, conectando RESET a 0 Voltios el

dispositivo está preparado para trabajar.

Conectaremos la salida del cristal de cuarzo de 16 MHz (reloj del

microprocesador) a la entrada de reloj del MM74HC4040 para a partir de

esta frecuencia, obtener las frecuencias de 8 MHz en la salida Q1 que

realiza una división por 2 y 500KHz en la salida Q5 que

realiza una división por 32, con las que se

excitarán el LM629 y el convertidor

analógico-digital ADC0808 respectivamente.

|

Reset

del sistema

|

|

Reset

del sistema

Hemos optado por un circuito especifico

para el caso, que en principio era el TL7705, pero ha sido sustituido

por un equivalente mas sencillo.

En aplicaciones con microprocesadores con entrada de /RESET activa en

bajo, el MAX7705 es compatible en funcionalidad y encapsulado con el

TL7705, salvo que no necesita componentes externos.

Aporta inmunidad ante "glitches" de alimentación y garantiza

un "delay" en el reset adecuado en el arranque (power-up).

Monitoriza la alimentación del microprocesador o sistema

digital implicado. El /RESET resulta valido para caídas de 1

V en la alimentación.

Provee un reset al sistema en arranque (power-up), por caída

de la alimentación (power-down) y situaciones de disturbio.

Cuando la alimentación baja del umbral establecido, la

salida /RESET es nivel bajo y mantiene al microprocesador en reset.

Esta salida /RESET volverá a nivel alto 280 mseg

después de que la alimentación supere el umbral

de reset.

Afecta tanto al microprocesador como al MPID.

Para conseguir un reset manual, se implementa un pulsador que une con

masa la línea de reset para ambos circuitos, útil

en emergencias o situaciones recomendadas por el indicador de errores.

|

|

|

|

|

Semblanza

Breve

Semblanza

Breve

![]()